On-going research projects

※ 차세대 반도체 메모리소자, 나노소자, MEMS 및 박막센서들에 적용을 위한 박막 및 적층구조의 나노식각공정에 의한 극미세 나노미터 패턴의 형성

개인연구사업(이공학개인기초연구: 2017.06~2020.05.30; 대학원생/연구원 모집중)

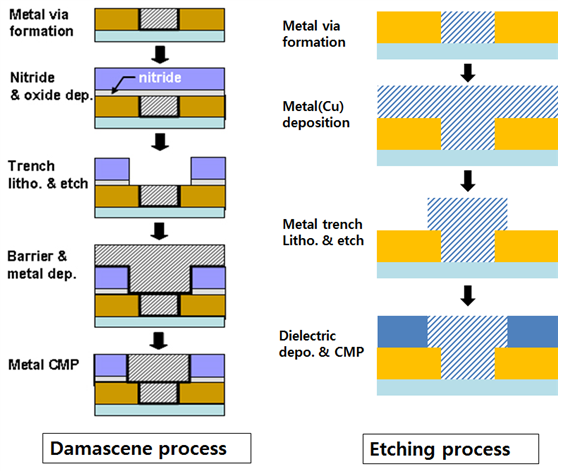

본 연구는 현존하는 메모리소자를 포함하여 차세대 반도체 메모리소자, MEMs(NEMs) 소자 및 각종 센박막센서들의 개발에 필요한 나노미터스케일의 극미세패턴의 형성을 위하여 새로운 나노식각공정을 개발하여 극미세패턴들을 형성하고자 하는 연구이며, 메모리소자들의 중요한 두 구성요소인 metal oxide semiconductor field effect transistor (MOSFET)와 capacitor의 극미세 나노미터패턴의 형성을 위한 식각공정을 개발하는 것이 그 중요한 예이다. 그 외에 본 연구의 핵심기술은 단위박막 및 적층구조의 미세 나노미터 패턴 형성을 위하여 나노식각기술이 필요로 하는 나노소자, MEMS, NEMS 및 박막센서소자의 제조에도 적용될 수 있다.

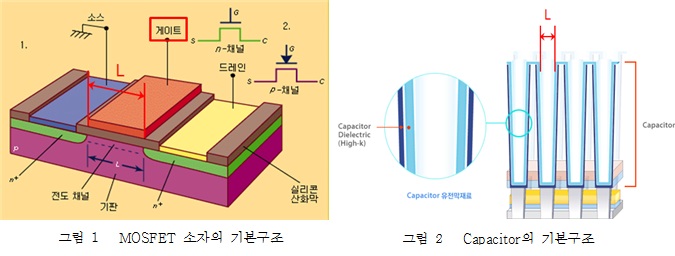

일반적으로 반도체 메모리소자는 메모리소자와 비메모리소자로 구분되고 메모리소자는 휘발성메모리소자와 비휘발성메모리소자로 구분된다. 비메모리소자는 시스템반도체, 개별소자 및 기타반도체소자로 구분된다. 이러한 MOSFET 디바이스의 구조에서 gate length (L)가 반도체소자의 전체 크기를 좌우하기 때문에 가장 중요한 dimension이다. 또한 유전체와 두 개의 전극으로 구성된 capacitor는 capacitor의 용량을 증가시켜서 메모리 용량을 크게 하기 때문에 작은 dimension에 작은 크기의 패턴 (L)으로 만들어져야 한다. 이러한 MOSFET 디바이스와 capacitor의 구조는 그림 1와 2에 각각 보여진다. 각 그림에서 MOSFET device의 gate length와 capacitor의 trench length가 L로 표현되었으며 바로 이 부분이 극미세 나노미터스케일로 식각되어져서 극미세 나노미터패턴이 형성되어져야하는 부분이다.

ITRS technology trend targets에 의하면 2017년에는 DRAM, Flash memory 소자들의 Half pitch가 32~45 nm로 예상되고 2020년에는 20~30 nm로 축소될 예정이다. 따라서 현재 반도체소자 제조공정에 있어서 breakthrough가 이루어져야 하는 부분은 (1) lithography 공정과 (2) etching 공정이다. 최근에는 lithography 공정보다 극미세 나노미터 패턴의 식각이 더욱 더 중요해지고 있다. 부연 설명하면 50 nm이하의 극미세패턴의 형성과 이에 대한 극미세패턴의 식각공정의 개발이 필수적이다. 향 후 2020년도에는 20~30 nm 이하의 극미세패턴의 형성을 위하여 나노식각공정이 필요로 할 것이다.

※ 자성물질의 박막 식각공정 및 차세대 자성메모리 소자 (MRAM) 개발

(산업통상자원부 산업융합원천기술개발사업; 2013.06~2018.05; 대학원생/연구원 모집중)

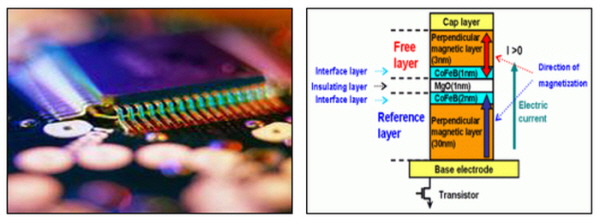

현재 전세계적으로 반도체 회사들의 합병 및 소멸 등의 구조변화가 시작되어 궁극적으로 세계 1, 2위의 메모리 반도체회사인 삼성전자와 하이닉스가 생존할 것으로 예상되고 있다. 각 회사들은 차세대 반도체 메모리소자의 개발을 위하여 경쟁적이고 집중적으로 국가의 지원을 받으며 연구하고 있다. 현재 연구 개발되고 있는 모든 차세대 반도체소자들은 소위 information technology(IT)와 nano technology(NT)를 이용하여 개발되고 있으며 그 가운데서 자성물질을 이용하는 자성 메모리 소자 (MRAM: Magnetoresistive Random Access Memory)는 기존의 비휘발성 메모리소자나 DRAM을 능가하는 고집적 초고속 차세대 메모리소자로서 현재 연구가 매우 활발히 진행되고 있다.

본 연구의 목표는 자성 반도체 메모리소자의 핵심 물질인 자성박막들의 패터닝 및 효율적인 식각을 위한 건식식각 (dry etching) 공정의 개발에 있다. 특히 식각가스의 개발 및 선택을 통해 보다 효율적인 표면화학반응을 유도하여 우수한 식각특성을 갖는 식각공정을 개발하고, 궁극적으로는 나노미터급 초미세패턴의 구현에 연구목표를 두고 있다. 현재 본 연구실에서는 산업통상자원부의 지식경제 기술혁신사업(산업융합원천기술개발사업)의 일환으로 진행되는 5년 간의 연구프로젝트에 참여하고 있다. 구체적으로 본 연구프로젝트에서는, 연세대, 포항공대 및 한국기초과학지원연구원과 함께 팀을 이루어, 반금속 물질을 이용한 고성능 MRAM 의 단위 소자인 MTJ(Magnetic Tunnel Junction) stack 의 소재 기술, 스위칭 기술, 식각 기술, 및 특성 평가 기술 등을 협력적으로 연구하고 있다. 특히 본 연구실에서는 식각 공정 연구에 대한 다년간의 경험과 노하우를 토대로, 반금속 물질 및 MTJ stack 의 효과적인 식각 기술 개발에 초점을 맞추어 집중적으로 연구를 진행하고 있다.