TSMC, 3㎚ 수율 문제로 곤욕.. AMD CPU 생산 차질 위기

2022.02.23 15:15

TSMC, 3㎚ 수율 문제로 곤욕.. AMD CPU 생산 차질 위기

입력 2022. 02. 23. 14:56자체 수율 기준 통과 못하면서 양산 차질

AMD 등 일부 고객사 기존 5㎚ 공정 적용

삼성전자, 6월부터 3㎚ 양산 계획대로 진행

전 세계 1위 반도체 파운드리(위탁 생산) 업체 대만 TSMC가 3㎚(나노미터·1㎚는 10억분의 1m) 공정 수율(생산품에서 양품이 차지하는 비율) 확보에 어려움을 겪고 있는 것으로 나타났다. TSMC는 올해 상반기 3㎚ 공정 양산을 시작할 계획이었지만 기대에 못 미치는 수율로 올해 하반기로 양산 계획을 연기한 상태다. 이런 상황에서 3㎚ 공정 수율이 자체 기준을 통과하지 못하면서 주요 고객사들의 내년 출시 신제품에도 기존 5㎚ 공정을 적용할 가능성도 커졌다.

23일 전자업계와 외신 등에 따르면 TSMC는 올해 하반기 양산을 목표로 3㎚ 공정 수율을 높이는 막바지 작업을 진행 중이지만 수율 확보에 어려움을 겪고 있다. 대만 정보기술(IT) 전문매체 디지타임스는 최근 “TSMC가 최적의 수율을 찾기 위한 다양한 작업을 진행하고 있지만, 목표로 하는 3㎚ 수율을 끌어내지 못하고 있다”라고 전했다.

이에 따라 TSMC의 3㎚ 공정을 적용하기로 한 일부 세트(완성품) 업체들은 기존 5㎚ 공정을 적용하기로 계획을 변경한 상태다. 미국 팹리스(반도체 설계회사) AMD가 대표적이다. AMD는 올해 출시할 노트북용 라이젠 6000 시리즈와 젠4(Zen 4) 기반 라이젠 프로세서에 3㎚ 공정을 적용할 계획이었는데, 최근 각각 6㎚, 5㎚ 공정을 적용하는 것으로 계획을 변경한 것으로 알려졌다. 디지타임스는 “낮은 3㎚ 공정 수율 때문에 AMD 등을 포함한 TSMC 고객사 일부가 로드맵을 수정하는 등 혼란을 겪고 있다”라고 했다.

TSMC가 3㎚ 공정 수율 문제를 겪는 정확한 이유는 공개되지 않았다. 다만 업계는 3000개 이상의 프로세스를 거치는 5㎚ 이하 공정의 난이도를 감안할 때 공정 개발에 어려움을 겪는 건 당연한 결과라고 보고 있다. 실제 3㎚ 공정의 경우 이전 세대인 5㎚와 비교해 집적소자 밀도는 50% 늘어난 반면 더 많은 비용과 더 높은 공정 기술 난이도를 요구한다.

TSMC가 3㎚ 공정에 집중하는 이유는 공정의 회로선폭이 좁을수록 고성능 반도체 부품을 더 작은 크기에서 만들 수 있기 때문이다. TSMC이 개발 중인 3㎚ 공정은 5㎚ 공정과 비교해 소비 전력은 7% 줄어든 반면 처리 속도는 15% 빠른 것으로 알려졌다.

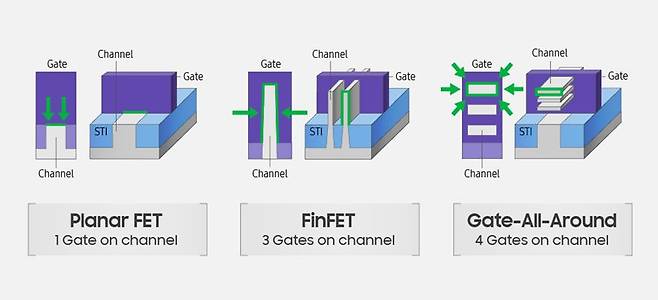

TSMC는 3㎚ 공정 개발을 위해 막대한 투자금을 투입하고 있다. 지난 2020년부터 1조5000억대만달러(약 61조5000억원)을 투자한 것으로 업계는 추산하고 있다. TSMC는 3㎚ 공정에 기존 미세 공정에 사용하는 돌고래 지느러미처럼 생긴 핀펫(FinFET) 구조를 그대로 적용한다는 계획이다. 핀펫은 기존 평면펫(PlanarFET) 대비 전력 효율성과 집적도가 우수하지만, 차세대 기술로 꼽히는 게이트-올-어라운드(GAA)과 비교해서는 전류 흐름의 미세하게 조절할 수 없다는 한계가 있다.

삼성전자는 올해 6월부터 3㎚ 양산을 계획대로 진행한다는 계획이다. 삼성전자는 지난해 10월 열린 ‘삼성 파운드리 포럼 2021′에서 이런 내용의 기술 로드맵을 공개한 바 있다. 삼성전자는 GAA 기술을 적용한 3㎚ 양산을 세계 최초로 시작해 TSMC와의 기술 경쟁에서 한발 앞서 나간다는 전략이다. 3㎚ 양산을 넘어 GAA로의 기술 전환에 속도를 내겠다는 것이다.

다만 삼성전자의 3㎚ 공정에 대해 우려의 시선도 있다. 삼성전자가 3㎚ 공정을 활용해 확보한 설계자산(IP) 수가 TSMC 대비 3분의 1 수준에 불과하기 때문이다. 설계자산은 새로운 기술을 활용해 개발한 칩 구조 및 설계 방식(아키텍처)을 말한다. 팹리스는 제품 개발 시간을 줄이기 위해 파운드리가 이미 개발해 놓은 설계자산을 이용하는 경우가 많은데, 설계자산이 부족할 경우 칩 개발의 효율성과 신뢰성을 높이는 데 추가적인 시간이 필요하다. 유안타증권에 따르면 지난 2020년 기준 삼성전자가 확보한 파운드리 설계자산은 7000~1만개로, TSMC(3만5000~3만7000개)와 비교해 크게 부족한 상태다.

한편 업계는 삼성전자와 TSMC가 GAA 기술을 동일하게 적용하는 2㎚ 공정에서 본격적인 기술 경쟁을 펼칠 것으로 판단하고 있다. 두 회사는 2025년을 목표로 GAA 기술을 적용한 2㎚ 공정 개발을 동시에 진행하고 있다. 디지타임스는 “삼성전자는 GAA 기술을 앞세워 TSMC를 추월하겠다는 전략을 펼치고 있다”라며 “TSMC 역시 GAA 기술을 적용한 2㎚ 공정 개발에 8000명 넘는 연구 인력을 투입하면서 기술 경쟁력을 키우고 있다”라고 했다.